# Digital PSU Plant Measurement

© Biricha Digital Power Ltd Parkway Drive Sonning-on-Thames RG4 6XG - UK www.biricha.com

Sept-2017

# **Biricha Digital Workshops**

DIGITA

- The following are just some slides from our workshops.

- Why not attend one our Analog or Digital PSU design workshops?

- We run them regularly in Germany and the US...

# **Digital Power & Digital PFC Workshop**

#### Day 1: Introduction to Digital Power

- Introduction to digital power, setting up digital power peripherals (PWMs, ADCs, etc.), number representation on MCUs

- Day 1 Lab exercises

**BIRICHA** DIGITAL

#### Day 2: Digital Voltage Mode Control

- Analog transfer function H(s), phase margin, gain margin and stability, analog compensator design, digital transfer functions, discrete time z & bi-linear transforms, digital compensator design

- Day 2 Lab exercise

#### Day 3: Digital Current Mode Control

- Digital peak current mode control, peak current mode model and compensator design slope compensation, sub-harmonic oscillations and stability

- Day 3 Lab exercises

#### Day 4: Digital PFC

- Step-by-step digital PFC control theory and operation, digital voltage loop current loop and voltage feed forward design, digital PFC software structure, linear difference equations and correct scaling, digital PFC implementation

- Day 4 Lab exercises

# **Analog Power & Analog PFC Workshop**

### Day 1: Introduction to PSU Design and Voltage Mode Control

- Topology selection guide, transfer functions and frequency domain design, Bode plots, poles and zeros, capacitor ESR, stability criteria, analog compensators, voltage mode control, Frequency response design

- Day 1 Lab exercises

**BIRICHA** DIGITAL

### Day 2: Peak Current Mode Control

- Peak current mode control, sub-harmonic oscillations, slope compensation, right hand plane zeros, Flyback PCMC controller, Transformer selection, non-isolated bias supplies, output filter design, snubber design

- Day 2 Lab exercise

#### Day 3: Isolated PSU and Bias Supply Design

- Isolated power supply design, isolated compensator design with TL431/LMV431, opto characteristics, programmable reference stability, real life design examples, isolated flyback design

- Day 3 Lab exercises

#### Day 4: Analog PFC

- Fundamentals of power delivery, step-by-step Analog PFC control theory, analog voltage loop, current loop and voltage feed forward design, PFC design and implementation

- Day 4 Lab exercises

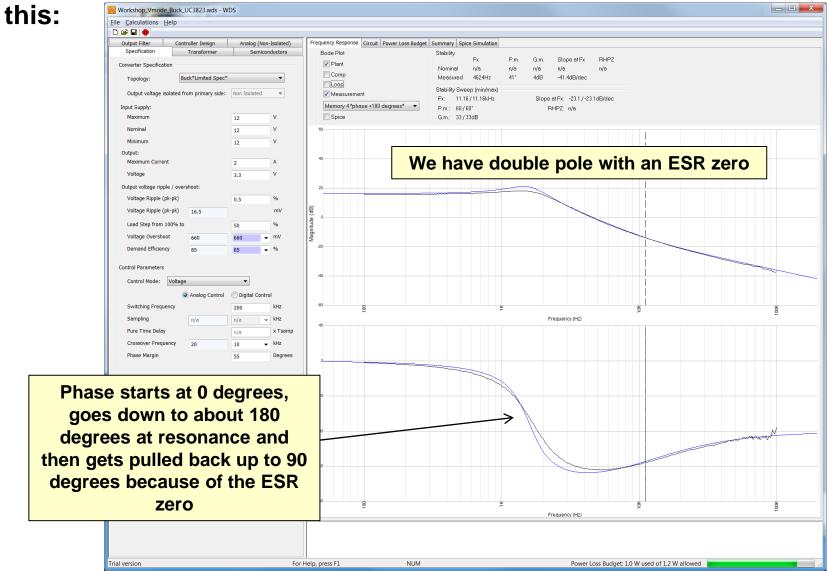

### Plant of a CCM Voltage mode Buck Converter typically looks like

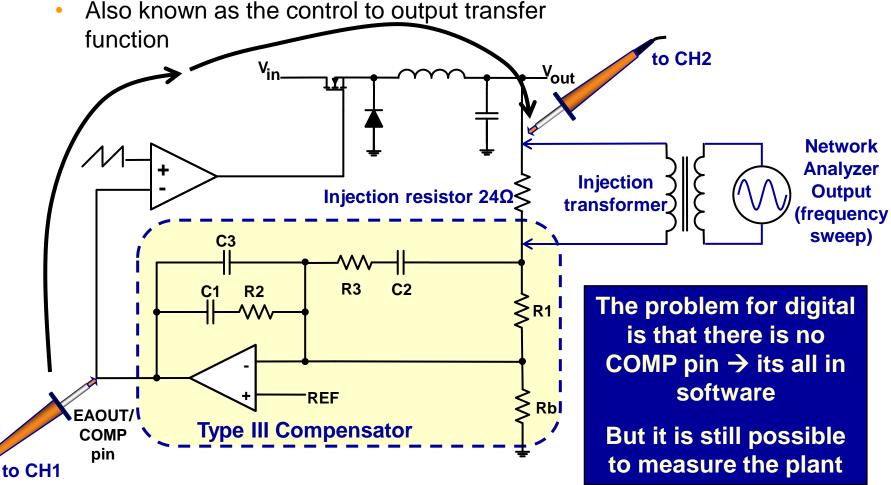

**Analog Plant Measurement**

• Measure the plant:

# **Measuring Plant of the Digital PSU**

- Our problem is that we can only measure the "loop"

- The power supply has some scaling factors

- Gain of the ADC potential divider

- Gain of the ADC itself

- Gain of the PWM block

- For simplicity let us assume that the gain of all of the above is 100

- So we have our plant scaled by 100

- If we now add a simple proportional compensator with a gain of 0dB (i.e. Kp = 1) and measure the "loop" we will in fact see the plant

- Because the compensator gain Kp is 0db it has no impact on the bode plot

- But our measurement will be off by a factor of 100

- So all we have to do is to set Kp to 1/100, then measure the loop and we will in fact see the plant

- We must still adjust the phase of the plant but we will talk about that shortly

### How to Calculate Kp so that the Overall Gain = 0dB

We need to set our Kp so that the overall gains are negated; for voltage mode set Kp to:

$$Kp = \left(\frac{1}{ADC \ Pot \ Scale \ Factor}\right) \times \left(\frac{ADC \ Range}{(2^{ADC \ bits} - 1)}\right) \times \left(\frac{PWM \ Period}{in \ Ticks}\right)$$

• Design Example:

DIGITA

- 200 kHz PWM with 12 bit ADC and a 4.096 GHz Hi-Res PWM clock and a potential divider with a Gain of 0.785

- Period = 20480 ticks & ADC quantization levels = 4095

$$Kp = \left(\frac{1}{0.785}\right) \times \left(\frac{3.3}{4095}\right) \times (20480) = 21.02$$

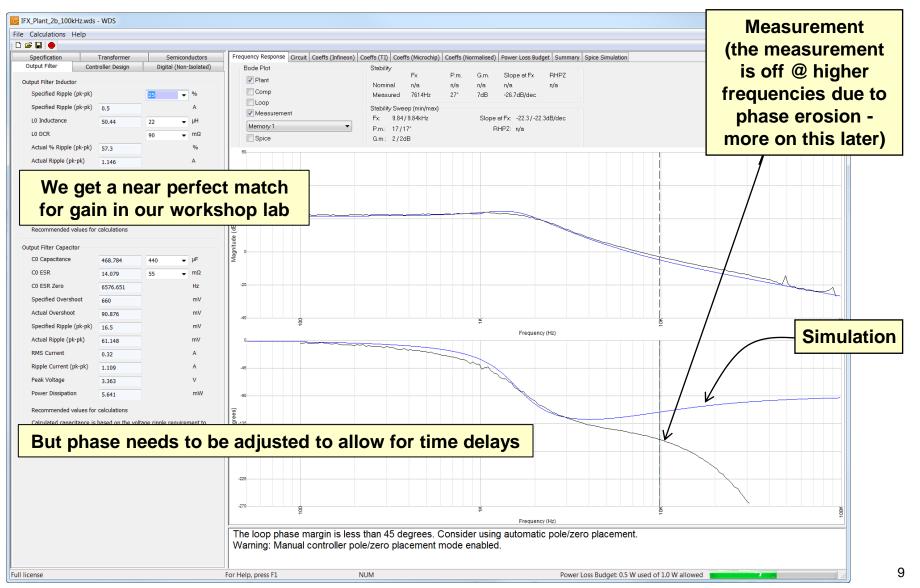

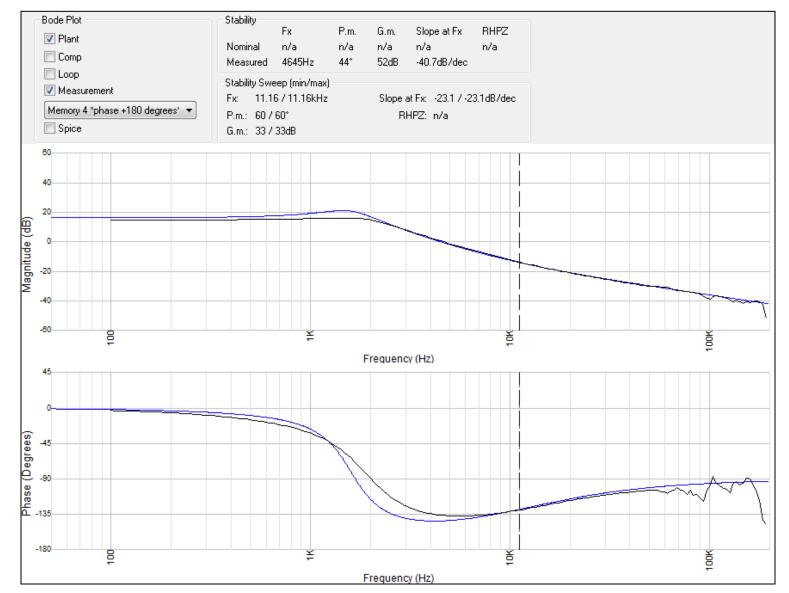

### **Real & Simulated Plant for One of Our Lab Power Stages**

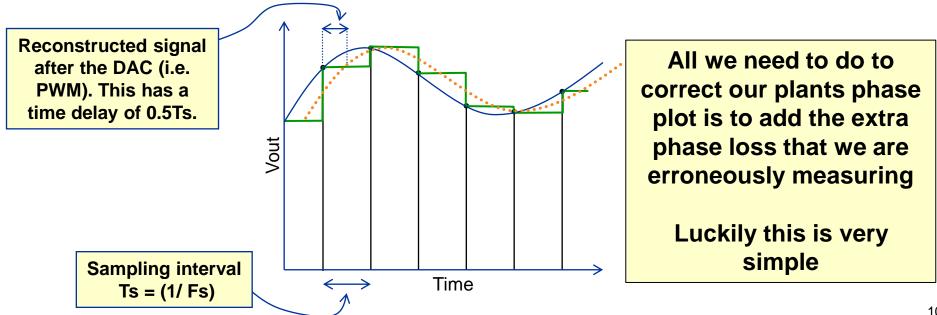

### **Phase Erosion in Digital World**

- Because our plant measurement is still going through sample and reconstruction, there

will be some phase loss → but in the case of the plant this is not real it is only an artifact

of the way that we are measuring.

- There are two mechanisms that introduce phase lag in to our digital power supply:

- The sampling and reconstruction process AND the time taken from the time we sampled our voltage to the time we carried out our calculations i.e. Time delay, Td

- The earlier we take our sample, the more the time delay and hence the phase loss

- Typically we sample at the beginning of the cycle so we have 1 Ts worth of pure time delay

## Phase Erosion in Digital World

• For a pure sine wave, phase delay  $\phi$  at a certain frequency *f* is given by:

$\phi = 360^{\circ} \times f \times Time \ Delay$

The sampling process and reconstruction introduces a time delay of 0.5xTs.

Therefore the phase margin erosion at 10kHz with a switching frequency of 200kHz

would be:

BIRICHA DIGITAL

$$\phi_{sampling} = 360^{\circ} \times f \times \frac{T_s}{2}$$

$(360^{\circ} \times 10 \text{ kHz} \times 5 \mu \text{s} / 2) = 9^{\circ}$

• Phase margin erosion at 10kHz due to calculation delay:

$$\phi_{calculation} = 360^{\circ} \times f \times k T_s$$

$(360^{\circ} \times 10 \text{ kHz} \times 5 \mu \text{s} \times 1 = 18^{\circ})$

Where:

k = in the number of sampling intervals (need not be an integer). Worst case scenario: we do the calculation at the beginning of the first sampling interval and update in the next; therefore k = 1

You can see that the measurement error in our phase can be "exactly" calculated from the above 2 equations and corrected on the plot

### **Real life Plant with Phase Corrected**

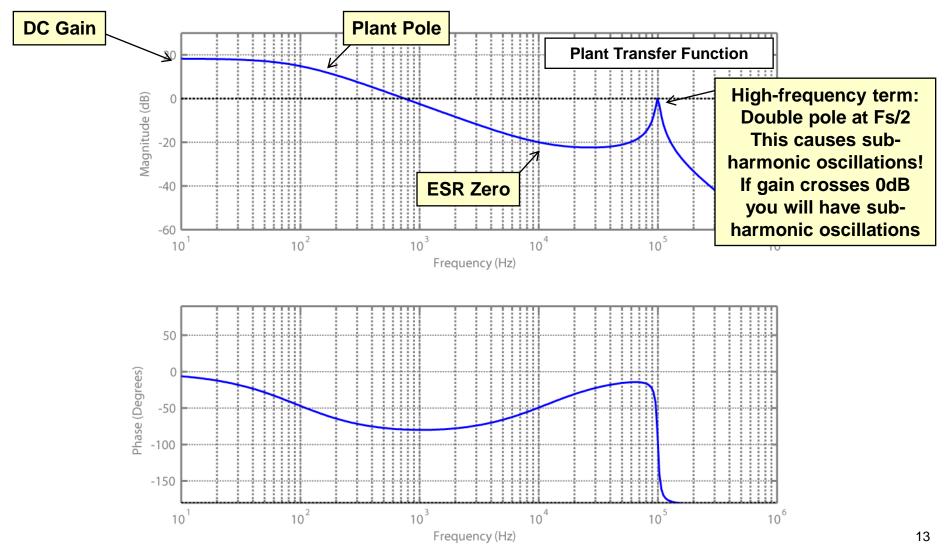

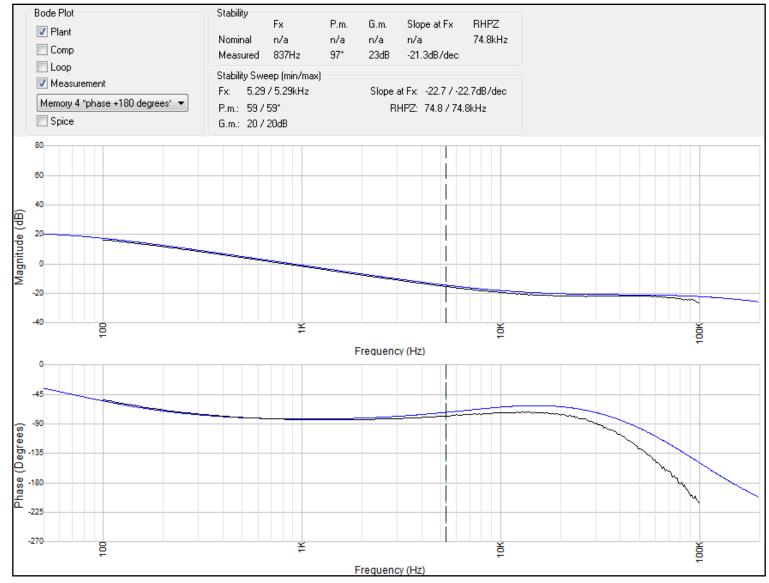

# **Peak Current Mode Plant**

**BIRICHA** DIGITAL

• The Bode plot of the peak current mode transfer function will look similar to this:

# Calculating the Scaling Factor Kp

- The procedure is exactly the same as voltage mode

- We have exactly the same gains as voltage mode but now we also need to take into consideration the scaling effects of the DAC

$$\mathsf{Kp} = \left(\frac{1}{ADC \ Pot \ Scale \ Factor}\right) \times \left(\frac{ADC \ Range}{(2^{ADC \ bits} - 1)}\right) \times \left(\frac{ADC \ Range}{(2^{ADC \ bits} - 1)}\right) \times \frac{(2^{DAC \ bits} - 1)}{DAC \ Range \ in \ Volts}$$

In the case of our Buck converter running an MCU with a 12 bit ADC and a 12 bit DAC:  $Kp = (1 / 0.785) \times (3.3 / 4095) \times (4095 / 3.3) = 1.27$

### **Real life Plant with Phase Corrected**

# Taken from Biricha's Digital Power Workshop

**Please visit:**

### **Important Notice**

**BIRICHA** DIGITAL

All material presented in this workbook, associated software, exercises, appendices and oral presentations made as part of all of Biricha Digital Power Ltd's workshops are for educational purposes only and are not intended for production or commercial applications and may contain irregularities and defects or errors. Furthermore, none of the material has been tested or certified by any government agency or industry regulatory organization or any other third party organization.

Biricha Digital Power Ltd makes no warranties or representations, express, implied or statutory, including any implied warranties of merchantability, fitness for a particular purpose, lack of viruses, lack of patent infringements, accuracy or completeness of responses and lack of negligence. Prior to using, incorporating or distributing any of the material that has been presented to you as part of this workshop in any commercial product, you must thoroughly test the product and the functionality in that product and be solely responsible for any problems or failures.

In no event shall Biricha Digital Power Ltd, or any applicable licensor, be liable for any special, indirect, incidental, or punitive damages, however caused, arising in any way out of your use of the material presented in this workshop. These excluded damages include, but are not limited to, cost of removal or reinstallation, procurement of substitute goods or services, outside computer time, labour costs, loss of data, loss of goodwill, loss of profits, loss of savings, loss of use or interruption of business or other economic loss.